Transistor Evolution: From Planar to CFET, 3D Integration Redefines Semiconductor Progress

For more than half a century, the semiconductor industry grew by following one simple rule: make transistors smaller. Shrinking feature sizes delivered higher performance, lower power, and lower cost per transistor. But today, this path has reached its physical and economic limit. The era of pure scaling is over, and a new era of structural innovation and 3D integration has begun.

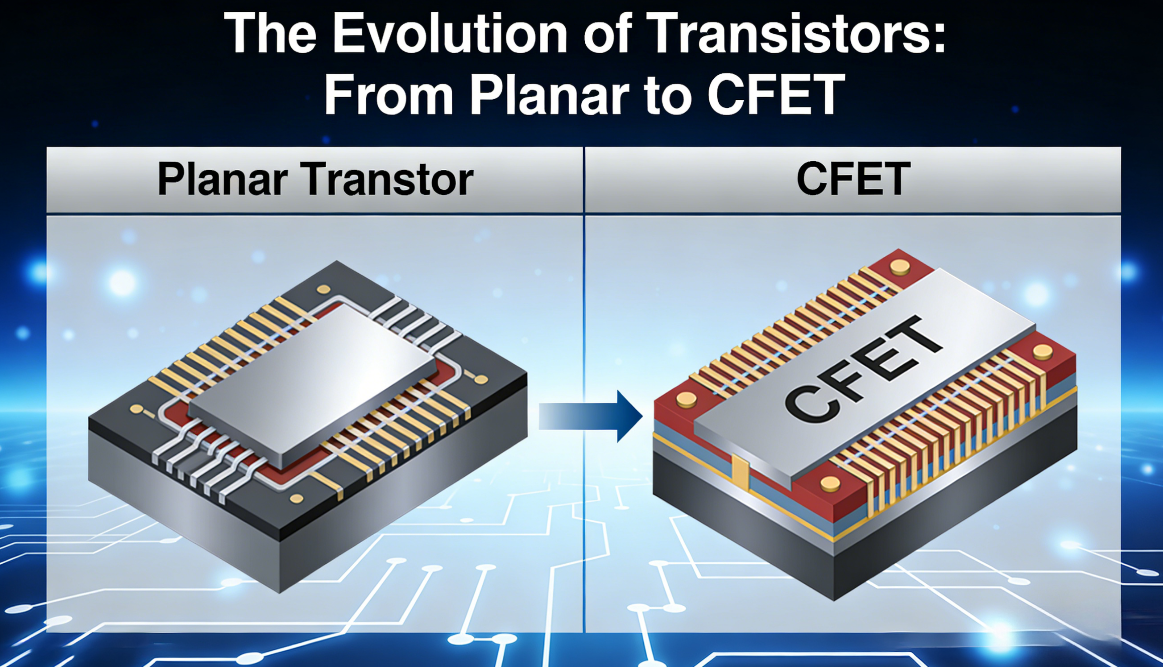

The transistor itself is undergoing a complete architectural revolution. From planar MOSFET to FinFET, from GAA nanosheet to CFET stacking, each step represents a shift from shrinking to rebuilding the transistor in three dimensions. This is not just incremental improvement—it is a complete redefinition of how chips deliver performance.

The Four Generations of Transistor Architecture

1. Planar Transistor (Traditional 2D)

The classic flat structure, where the gate controls the channel from above. It dominated from the early days down to 40nm and 28nm. As dimensions shrank further, leakage current and electrostatic control became unsolvable problems.

2. FinFET (3D Gate Control)

The channel becomes a vertical “fin”, with the gate wrapping around three sides. This drastically improves electrostatic control, reduces leakage, and enables scaling down to 7nm, 5nm, and even 3nm. FinFET became the foundation of the modern high-performance chip era.

3. GAA Nanosheet (Gate-All-Around)

At 2nm and below, FinFET hits its limit. GAA replaces the fin with stacked horizontal nanowires or sheets, fully surrounded by the gate. It delivers better control, lower power, and higher drive current. GAA is now the mainstream structure for 2nm-class chips across TSMC, Samsung, and Intel.

4. CFET (Complementary FET)

The next frontier: stacking NMOS and PMOS vertically. CFET packs two transistors into the footprint of one, drastically reducing area and improving density. It is the ultimate evolutionary end of transistor scaling before true 3D system integration takes over.

Why Scaling Alone No Longer Works

- Process costs rise exponentially at each new node

- Quantum leakage and physical constraints harden limits

- Interconnect delay and power consumption overtake transistor speed

- Large monolithic chips suffer from low yield and high cost

The industry has realized: performance no longer comes from smaller transistors. It comes from better connections, smarter architecture, and vertical integration.

The New Era: Three Layers of 3D Innovation

Semiconductor progress is now defined by three dimensions of 3D design:

- 3D Transistor: FinFET, GAA, CFET – building the transistor vertically

- 3D Device Stacking: Memory on logic, hybrid bonding, SRAM stacking

- 3D System Integration: Chiplet, 2.5D/3D packaging, interposer-based integration

Together, they form the 3D×3D×3D era: the transistor, the device, and the system all become three-dimensional.

DTCO: The New Core Competence

As scaling ends, Design Technology Co-Optimization (DTCO) becomes critical. It means co-designing architecture, transistor structure, metal routing, and packaging from the start. The strongest companies are no longer just process leaders—they are system-level integrators.

Wiring efficiency, power delivery, thermal design, and bandwidth density now determine real product performance.

AI Is the Ultimate Driving Force

AI and high-performance computing demand unprecedented bandwidth, energy efficiency, and density. These requirements cannot be met by traditional scaling. They require:

- Ultra-high-bandwidth memory-compute interconnect

- Extreme energy efficiency per operation

- Massive parallelism and dense integration

AI has forced the entire industry to abandon pure scaling and embrace full 3D heterogeneous integration.

Conclusion: The Future Is Not Smaller, It Is Higher

The age of shrinking transistors is fading. The future of semiconductors is not about making devices smaller—it is about building systems higher, denser, and more intelligently connected.

From Planar to FinFET to GAA to CFET, the transistor has completed its evolution. The next battle will be fought in 3D integration, advanced packaging, and system-level design. This is where the next decade of semiconductor leadership will be decided.